# **DIGITAL INDUSTRIES SOFTWARE**

# 将 2.5D/3DIC 物理验证提升到 更高水平

# **Executive summary**

随着封装设计的发展,验证要求和挑战如影相随。设计人员在处理 2.5/3D IC 设计中的多裸片、多小芯片堆叠配置时,现在可以使用增强型 Calibre 3DSTACK 物理验证检查来验证裸片对齐情况,以实现正确的连接关系和电气行为。设计团队可利用 Calibre 3DSTACK 预检模式,在调用 Calibre 3DSTACK signoff 运行之前查找并更正基本实现差错和系统性错误,从而消除不必要的调试迭代,加快整体封装验证流程。

Authors: John Ferguson and Armen Asatryan

# 简介

高密度先进封装 (HDAP) 在各种最终用户应用中的采用率持续攀升。使用中介层(硅或有机)的 2.5D 集成电路 (IC) 设计通常针对高端应用,如军事、航空航天和高性能计算,而类似台积电集成扇出 (InFO) 封装这样的 3D 扇出封装方法,则更侧重于手机等大规模消费应用(图 1)。此外,所有主流设计公司、晶圆代工厂和封测代工厂(OSAT) 都在投资新一代技术——使用硅通孔 (TSV) 和混合键合的真正裸片堆叠。

图 1.HDAP 技术。

伴随 HDAP 设计的使用,电子设计自动化 (EDA) 对 HDAP 验证的支持也在同步发展。 HDAP 验证解决方案解决了与 HDAP 验证相关的多个问题:

- 用于封装设计的装配设计套件 (ADK) 的开发 [1,2]

- 用于先进封装的装配级 LVS 的概念和要求 [3,4]

- 用于先进封装的布线后模拟仿真与数字静态时序分析 (STA) 流程 [5]

- 在考虑裸片、封装和裸片/封装接口寄生效应的同时生成 HDAP 系统级连接关系的选项 [6]

- 解决 3DIC 验证方法中面临的数据不完整挑战的验证选项 [7]

最简单形式的 HDAP 物理验证由两项主要要求组成:

- 连接关系:验证多个裸片通过封装/中介层布线正确连接

- 对齐:验证多个裸片在封装/中介层顶面按预期对齐

2.5/3DIC 物理验证的这项基本定义通常被认为是公认的,这意味着最终客户和生态系统合作伙伴(晶圆代工厂/OSAT 和 EDA 公司)都知道并理解基本要求。事实上,生态系统合作是开发 3DIC 物理验证设计套件作为封装 ADK 起点的驱动力。

但是,随着 3DIC 技术的进步和设计公司不断构建更复杂的 HDAP 设计,物理验证需求日渐扩大。这类先进物理验证要求将 3DIC 物理验证提升到更高水平。为了跟上步伐,EDA 供应商正在扩展其 3DIC 验证工具和策略方面的能力。

# Calibre 3DSTACK 物理验证

Calibre® 3DSTACK 工具是专为 2.5/3DIC 和封装设计而开发的自动化物理验证系统 [8]。它已在整个生态系统中被 OSAT、晶圆代工厂和设计公司广泛采用,并支持许多 裸片封装设计(包括西门子自己的硬件加速器技术)成功进入市场,同时避免了昂贵的重新设计。利用 Calibre 3DSTACK 工具,设计人员可以对任意工艺节点的完整多裸片系统执行 signoff 设计规则检查 (DRC) 和 LVS 验证,而无需中断当前的工具流程,也不需要新的数据格式。

作为持续提高工具和验证过程的效率及准确性的举措之一,关键的对齐检查功能得到了强化,并增加了创新的预检模式,以支持设计人员在运行 signoff 之前查找并消除选定的错误。

# 裸片/中介层对齐检查

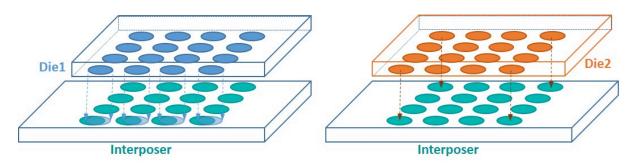

对齐检查是 3DIC 验证期间执行的基本步骤之一。Calibre 3DSTACK 重叠和中心检查都能验证位于封装/中介层顶面的多个裸片是否按预期对齐。重叠检查确定两个交互裸片的焊盘之间是否有足够的重叠,而中心检查则分析焊盘对的中心,以检查是否有任何错位(图 2)。虽然这两种检查都能准确涵盖对齐检查的基本要求,但调试和修复这些检查所识别的错误可能颇具挑战性。

图 2.基本重叠和中心检查。

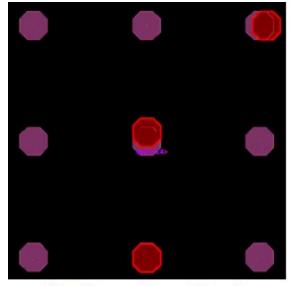

### 中介层至裸片检查中的误报

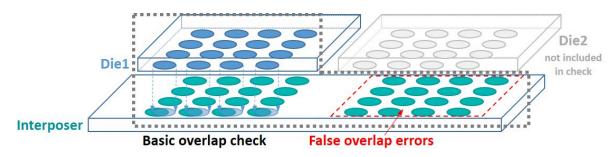

对于在中介层顶面有多个裸片的 2.5D 装配或设计而言,基本重叠或中心检查一次仅检测/检查一个裸片,这可能导致实际被其他裸片覆盖的中介层焊盘出现误报(图 3)。

图 3.基本重叠检查中由于布置在中介层上但未包括在检查范围内的额外裸片而导致的误报。

增强型重叠和中心检查会自动检测与给定中介层交互的所有裸片,并且一次检查中介层焊盘与所有裸片焊盘的重叠/中心,从而消除这类误报(图4)。

图 4:添加智能功能消除了增强型重叠和中心检查由于多个裸片而导致的误报。

虽然基本检查和增强型检查具有相同的名称,但它们的语法不同。当一个装配中的两个交互级别只有一个裸片时,基本检查功能就足够了。但是,当中介层的同一级别 (即同一层中) 具有多个裸片时,应使用增强型检查。

# 调试中心检查错位错误

即使没有误报,调试中心检查错误也可能颇具挑战性,尤其当违规是由于轻微错位引起时。设计人员必须手动计算两个焊盘上的凸块中心,并测量差异以纠正错误。

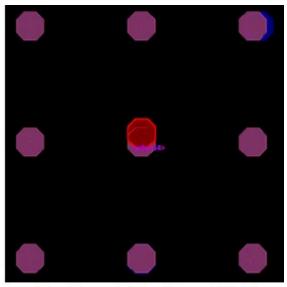

为了简化中心检查错位错误的调试,Calibre 3DSTACK 为增强型中心检查提供了一种功能,生成指向用于测量的焊盘中心的特殊标记/提示,从而使错位在调试过程中变得明晰可见。

Highlighted error

Markers/hints for misalignment error

图 5.用于中心检查错位错误的标记有助于设计人员快速、准确地调试这些错误。

#### 用于带有文本的凸块的中心检查

传统上,设计团队会对指定裸片层的所有凸块/焊盘应用中心检查。但是,设计人员通常对检测带有文本的凸块中的错位特别感兴趣,这些凸块代表用于连接关系目的的管脚。

基本的中心检查不会执行这种类型的筛选,但设计人员可利用增强型中心检查,仅对带有文本的焊盘应用中心检查(图 6)。

Basic centers check

Centers check applied only on texted pads

图 6.设计人员可利用选择性筛选,仅对带有文本的焊盘应用中心检查。

# 3DIC 物理验证的数据准备

许多设计团队在 3DIC 验证流程中面临的挑战之一是,有效地管理不完整的数据和不正确的设置。这些问题可能各不相同,包括:输入中缺失数据,缺失对齐检查导致未被检测到的裸片到裸片对齐问题,以及系统级设计缺陷导致高错误数的系统性问题。系统性问题包括版图和源之间的管脚名称差异,或规则集中的文本附件语句缺失/定义错误等,这两种问题都会产生虚假的连接关系检查违规,需要进行不必要的调试迭代。

为了极大限度减少这些影响,Calibre 3DTSTACK 工具提供了一种创新的预检模式,设计人员可利用此模式在调用 Calibre 3D STACK signoff 运行之前捕获任何明显的设置/数据问题。尽管裸片在 3D 堆叠阶段之前已完成流片,但这种预检模式有助于在 Calibre 3DSTACK signoff 运行前捕捉任何早期、系统性的系统级/多裸片集成问题。Calibre 3DSTACK 预检模式包括多个用于检测数据和设置问题的过程。

#### ###源网表检查

源网表检查检测并报告源网表语法问题,并验证源到版图的正确映射。版图与源裸片之间缺少映射定义或映射定义不正确,可能导致流程终止和/或产生虚假的连接关系检查违规。

#### ###检查带有文本的焊盘

在 Calibre 3DSTACK 规则集中,设计人员定义了与表示裸片管脚的层之间的文本关联。每个管脚由端口-焊盘(用户指定的层上的几何形状)表示,并附有相同的文本标签。预检模式可检测多个与焊盘相关的问题

#### :- 未附加文本的焊盘

- 附加多个文本的焊盘

- 与任何焊盘无关的文本标签(与用户指定的管脚层的几何形状没有任何重叠)

这些问题如未解决,将会在 Calibre 3DSTACK signoff 运行中造成连接关系检查违规。

# ###缺失或额外端口检查

缺失或额外端口检查确定版图和源网表中的裸片管脚是否匹配,并报告版图中的任何 缺失或额外端口。造成这种错误的原因有多种:规则集中不正确的文本关联语句,缺 失焊盘,管脚名称拼写错误等。在早期检测并修复这些问题,可大幅减少 signoff 运行 期间的调试时间。

#### ###规则集覆盖率

规则集覆盖率分析裸片堆叠(装配)并自动检测裸片到裸片交互。如果规则集中缺失了任何裸片到裸片交互,它会建议逐一检查每个裸片或交互的裸片对。这些建议可确保规则集针对装配验证提供完全覆盖,防止未被检测到的任何违规(对齐情况或连接关系)。

# ###中介层电源和接地短路检查

中介层电源和接地短路检查可针对用户为中介层裸片指定的电源和接地网络应用开路/短路检查,以帮助设计人员更快地找到根本原因。电源/接地连接关系检查中的违规往往是最难调试的,因为电源和接地网络会穿过装配中的所有裸片,并覆盖设计中的很大面积,这使得查找真正导致短路的几何形状成为一个真正的挑战。

解决所有问题并应用 Calibre 3DSTACK 预检模式报告的所有建议,有助于设计团队大幅缩短 signoff 运行中的调试时间。

# 结语

随着封装设计的持续发展,验证要求和挑战如影相随。设计人员即使在处理最复杂的多裸片、多小芯片堆叠配置时,也可以使用 Calibre 3DSTACK 3DIC 验证的增强检查功能,快速轻松地验证物理裸片是否正确布局,以确保正确的连接关系和电气行为。设计团队可利用预检模式,在调用 Calibre 3DSTACK signoff 运行之前查找并更正基本实现差错和系统性错误,从而消除不必要的调试迭代,并加快整体封装验证流程。

此外,与西门子 Xpedition Package Designer (XPD) 和 Xpedition Substrate Integrator (XSI) 工具的集成有助于加快实现速度,与此同时,与业界领先的寄生参数提取工具的结合,还可以捕获裸片或封装接口之间的耦合 [9,10]。通过扩展其他传统 IC 验证工具,如可靠性验证,来识别和解决封装问题,设计公司能够进一步提高其产品的市场价值 [11-13]。展望未来,与布局规划、布局布线、可靠性验证以及电源、热和应力分析等其他工具的集成,将为 HDAP 行业提供一种自动化程度更高的设计到制造模式。

商标名 OASIS 是位于加州 Alamo 的 Thomas J. Grebinski 在美国的注册商标,并授权 SEMI 独占使用。

# References

- 1.J. Ferguson, T. Ramadan, "The Future of Package Design Verification: Assembly Design Kits," Siemens Digital Industries Software.Oct. 2015. <a href="https://resources.sw.siemens.com/en-US/white-paper-the-future-of-package-design-verification-assembly-design-kits">https://resources.sw.siemens.com/en-US/white-paper-the-future-of-package-design-verification-assembly-design-kits</a>

- 2.K. Rinebold, K. Felton, "Implementing High-Density-Advanced Packaging for OSATs and Foundries," Siemens Digital Industries Software.May 2017. <a href="https://resources.sw.siemens.com/en-us/white-paper-implementing-high-density-advanced-packaging-for-osats-and-foundries">https://resources.sw.siemens.com/en-us/white-paper-implementing-high-density-advanced-packaging-for-osats-and-foundries</a>

- 3.Tarek Ramadan, "Package designers need assembly-level LVS for HDAP verification," Siemens Digital Industries Software.Dec. 2017. <a href="https://resources.sw.siemens.com/en-US/white-paper-package-designers-need-assembly-level-lvs-for-hdap-verification">https://resources.sw.siemens.com/en-US/white-paper-package-designers-need-assembly-level-lvs-for-hdap-verification</a>

- 4.Tarek Ramadan, "A deep dive into HDAP LVS/LVL verification," Siemens digital Industries Software.Sept. 2019. <a href="https://resources.sw.siemens.com/en-US/white-paper-a-deep-dive-into-hdap-lvs-lvl-verification">https://resources.sw.siemens.com/en-US/white-paper-a-deep-dive-into-hdap-lvs-lvl-verification</a>

- 5. Tarek Ramadan, "System-level, post-layout electrical analysis for high-density advanced packaging," Siemens Digital Industries Software. Sept. 2018. <a href="https://resources.sw.siemens.com/en-us/white-paper-system-level-post-layout-electrical-analysis-for-high-density-advanced">https://resources.sw.siemens.com/en-us/white-paper-system-level-post-layout-electrical-analysis-for-high-density-advanced</a>

- 6.Keith Felton, "Using Calibre for Advanced IC Packaging Verification and Signoff," Siemens Digital Industries Software.Feb. 2021. <a href="https://resources.sw.siemens.com/en-US/white-paper-using-calibre-for-advanced-ic-packaging-verification-and-signoff">https://resources.sw.siemens.com/en-US/white-paper-using-calibre-for-advanced-ic-packaging-verification-and-signoff</a>

- 7. Tarek Ramadan, "Crossing the Chasm: Bringing SoC and Package Verification Together with 3DSTACK," Siemens Digital Industries Software.Jan. 2017. <a href="https://resources.sw.siemens.com/en-US/white-paper-crossing-the-chasm-bringing-soc-and-package-verification-together-with">https://resources.sw.siemens.com/en-US/white-paper-crossing-the-chasm-bringing-soc-and-package-verification-together-with</a>

- 8."Calibre 3DSTACK," Siemens Digital Industries Software.2015. <a href="https://resources.sw.siemens.com/">https://resources.sw.siemens.com/</a><a href="https://resources.sw.siemens.com/">en-US/fact-sheet-calibre-3dstack</a><a href="https://resources.sw.siemens.com/">https://resources.sw.siemens.com/</a><a href="https://resources.sw.siemens.com/">en-US/fact-sheet-calibre-3dstack</a><a href="https://resources.sw.siemens.com/">https://resources.sw.siemens.com/</a><a href="https://resources.sw.siemens.com

- 9.J. Ferguson, K. Felton, "Implementing Fan-Out Wafer Level Packaging (FOWLP) with the HDAP Flow," Siemens Digital Industries Software.June 2017. <a href="https://resources.sw.siemens.com/en-US/">https://resources.sw.siemens.com/en-US/</a> white-paper-implementing-fan-out-wafer-level-packaging-fowlp-with-the-hdap-flow

- 10.K. Rinebold, J. Ferguson, K. Felton, "Surviving the three phases of high density advanced packaging design," Siemens Digital Industries Software. Aug. 2018.

- https://resources.sw.siemens.com/en-US/white-paper-surviving-the-three-phases-of-high-density-advanced-packaging-design

- 11. Dina Medhat, "Automated ESD protection verification for 2.5D and 3D ICs," Siemens Digital

Industries Software.June 2021. <a href="https://resources.sw.siemens.com/en-US/white-paper-automated-esd-protection-verification-for-2-5d-and-3d-ics">https://resources.sw.siemens.com/en-US/white-paper-automated-esd-protection-verification-for-2-5d-and-3d-ics</a>

12.Dina Medhat, "2.5D/3D IC latch-up prevention: an automated verification strategy," Siemens Digital Industries Software.July 2021. <a href="https://resources.sw.siemens.com/en-US/white-paper-2-5d-3d-ic-latch-up-prevention-an-automated-verification-strategy">https://resources.sw.siemens.com/en-US/white-paper-2-5d-3d-ic-latch-up-prevention-an-automated-verification-strategy</a>

13.John Ferguson, "Is 3D-IC the next big profit driver?," EE Times.Oct 23, 2018.

<a href="https://www.eetimes.com/is-3d-ic-the-next-big-profit-driver/#">https://www.eetimes.com/is-3d-ic-the-next-big-profit-driver/#</a>

#### **Siemens Digital Industries Software**

### 办事处

# 总部

Granite Park One 5800 Granite Parkway Suite 600 Plano, TX 75024 USA +1 972 987 3000

# 美洲

Granite Park One 5800 Granite

Parkway

Suite 600

Plano, TX 75024 USA

+1 314 264 8499

# 欧洲

Stephenson House Sir William Siemens Square Frimley, Camberley Surrey, GU16 8QD +44 (0) 1276 413200

#### 亚太地区

Unit 901-902, 9/F Tower B, Manulife Financial Centre 223-231 Wai Yip Street, Kwun Tong Kowloon, Hong Kong +852 2230 3333

For additional numbers, click here.

#### 关于我们

西门子数字化工业软件通过 Siemens Xcelerator 数字商业平台的软件、硬件和服务,帮助各规模企业实现数字化转型。西门子全栈式工业软件和全面的数字孪生可助力企业优化设计、工程与制造流程,将创新想法变为可持续的产品,从芯片到系统,从产品到制造,跨越所有行业,创造数字价值。西门子数字化工业软件 – 加速转型。

#### About the authors

### John Ferguson

John Ferguson 是西门子数字化工业软件 Calibre DRC 应用部门产品管理总监。John 在物理设计验证领域拥有丰富的经验。他拥有麦吉尔大学物理学学士学位、马萨诸塞大学应用物理学硕士学位和俄勒冈理工学院电气工程博士学位。

### **Armen Asatryan**

Armen Asatryan 是西门子数字化工业软件旗下西门子 EDA 的 Calibre 平台研发技术负责人。在加入西门子 EDA 之前,他曾在 EDA 初创公司担任多个研发管理职位,专注于合格率分析工具的数据库管理以及与 P&R 环境的流程集成。Armen 拥有面向计算机科学的应用数学硕士学位,以及亚美尼亚国家科学院信息学和自动化问题研究所工程博士学位。